大阪大学开发用于最大程度地优化AI任务的FPGA计算设备

大阪大学的研究人员构建了一种新设备,用户可以对其进行定制,以最大程度地提高AI应用的效率。

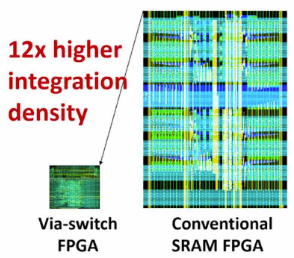

与当前的可重布线硬件相比,该计算设备已构建有现场可编程门阵列(FPGA),可将电路密度提高十二倍。它还可将能耗降低多达80%。人们认为,这些进步可能会导致更灵活的AI解决方案,既可以提高性能,又可以减少能耗。

为什么需要效率

人工智能正在迅速对我们的世界产生更大的影响。随着5G,物联网的出现,以及人们认为5G的后续第六代移动网络(6G)几乎完全由AI提供支持,对开发能够不仅跟上潮流的计算解决方案的需求日益增长。技术,但也适用于不同的AI应用程序和流程。这样一来,研究将有助于解决当今最紧迫的问题之一-气候紧急状态(或对于愤世嫉俗的人而言,气候变化)。

培训人工智能是一个耗费大量精力的密集过程。最近的估计表明,训练一块人工智能可以使用多达284吨的二氧化碳-相当于一辆普通汽车的一生排放量的五倍。

这也不是说受过训练的AI的例子很少也没有。他们无处不在。Google Translate,OpenAI的GPT-2文本生成器,Uber这样的拼车应用,垃圾邮件过滤器以及Nest和Ring等智能家居设备都非常依赖AI和深度学习。尽管像亚马逊这样的公司在风能和太阳能发电场上进行投资,而谷歌与可再生能源供应商建立长期协议,都是朝着正确方向迈出的一步,但这还远远不够。

优化计算机电路以实现高效的AI处理

因此,复杂的算法需要大量的计算能力。这意味着更高的能源消耗,因此也意味着更大的碳足迹。但是,如果可以为每个给定的AI任务重新连接系统以优化计算机电路,我们将实现更高的能效水平。

尽管外行用户可能将“电路”看作是处理器中固定的物理晶体管和逻辑门(固定的),但FPGA是专用的逻辑元件,可以实时(或“现场”)重新布线,因此“现场-由用户定制和动态应用。而这正是大阪研究人员所做的。

研究团队使用了非易失性“通孔开关”,它们一直保持连接状态,直到操作员决定需要对其进行重新配置。通过使用一种新颖的纳米制造方法,该团队能够将更多的十二倍的元件包装成网格状的“交叉开关”布局,从而缩短了电子信号必须传播的距离,从而减少了功耗,最多可减少80%。

研究论文的主要作者Masanori Hashimoto表示:“我们基于现场可编程门阵列的系统具有非常快的设计周期。如果需要,可以每天对其进行重新编程,以使每个新的AI应用程序获得最大的计算能力。”

通过使用通孔开关,研究团队还无需包括其他FPGA器件所需的编程硅区域。